Applied Materials New eBeam Metrology System for High-NA EUV Lithography.

New VeritySEM® 10 system delivers industry-leading resolution and imaging speed to help chipmakers accelerate process development and maximize yield in high-volume manufacturing

SANTA CLARA, Calif., Feb. 28, 2023 – Applied Materials, Inc. today introduced a new eBeam metrology system specifically designed to precisely measure the critical dimensions of semiconductor device features patterned with EUV and emerging High-NA EUV lithography.

Chipmakers use CD-SEMs (critical dimension scanning electron microscopes) to take sub-nanometer measurements of patterns once a lithography scanner transfers them from a mask to a photoresist. These measurements continuously calibrate lithography process performance to ensure the patterns are correct before they are etched into the wafer. CD-SEMs are also used after etch to correlate intended patterns with on-wafer results. CD-SEMs thereby help control the etch process and enable a feedback loop between lithography and etch that gives engineers highly correlated data sets for holistic process tuning.

Measuring the critical dimensions of semiconductor device features becomes more challenging as photoresists get thinner with EUV and especially High-NA EUV. To capture high-resolution images that provide accurate, sub-nanometer measurements, the CD-SEM must be able to precisely apply a narrow eBeam to the small area occupied by the extremely thin photoresist. eBeam energy interacts with photoresists, and if the landing energy is too high, the resist will shrink, distorting the pattern and creating errors. Conventional CD-SEMs cannot produce beams narrow enough to create high-resolution images at landing energies low enough to minimize interactions with the delicate High-NA photoresist.

Introducing the VeritySEM® 10 CD-SEM Metrology System

Applied’s new VeritySEM 10 system features a unique architecture that enables low landing energy at 2X better resolution compared to conventional CD-SEMs. It also provides a 30-percent faster scan rate to further reduce interaction with the photoresist and increase throughput. The system’s industry-leading resolution and scan rate provide improved control of EUV and High-NA EUV lithography and etch processes to help chipmakers accelerate process development and maximize yield in high-volume manufacturing.

The VeritySEM 10 system is also being adopted by chipmakers for critical dimension metrology applications in 3D designs, including Gate-All-Around (GAA) logic transistors and 3D NAND memories, where the system’s back-scattered electrons enable high-resolution imaging of deep structures. Among the applications for GAA chips, the VeritySEM 10 is being used to measure and characterize the selective epitaxy process which is key to transistor performance. For 3D NAND memories, the system provides a large field of view and high depth of focus to measure entire staircase interconnect structures and help tune etch process recipes.

“The VeritySEM 10 system is a breakthrough in CD-SEM technology that solves the metrology challenges of major technology inflections that will shape the industry in the years ahead,” said Keith Wells, Group Vice President of Imaging and Process Control at Applied Materials. “The system’s unique combination of low landing energy, high resolution and faster imaging speed helps pave the way to High-NA EUV, Gate-All-Around transistors and high-density 3D NAND.”

The VeritySEM 10 system is receiving strong commercial interest from leading logic and memory customers, with more than 30 systems shipped over the past year. Multiple customers have selected the system as the development tool of record for GAA transistors. All leading 3D NAND customers have chosen the system as the development and process tool of record, and multiple DRAM customers have selected it as the process tool of record.

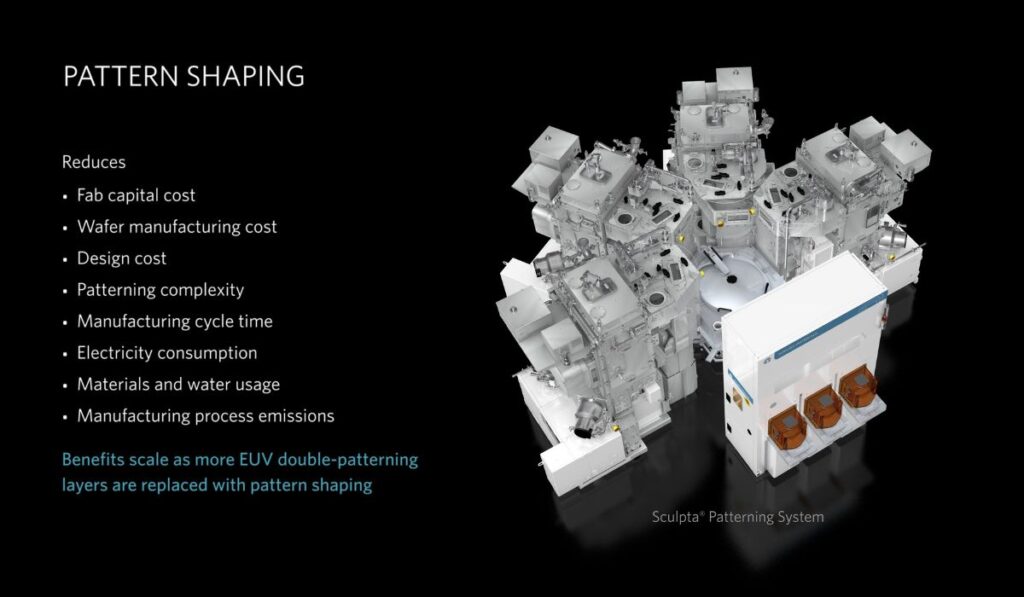

Centura® Sculpta® patterning system

Applied Materials, Inc also unveiled a breakthrough in patterning technology that allows chipmakers to create high-performance transistors and interconnect wiring with fewer EUV lithography steps, thereby lowering the cost, complexity, and environmental impact of advanced chipmaking.

Customers increasingly use EUV double patterning to print chip features smaller than the resolution limits of EUV to optimize chip area and cost. Using EUV double patterning, chipmakers split a high-density pattern in half and produce two masks that adhere to the resolution limits of EUV. Both halves of the pattern are combined on intermediate patterning films and then etched into the wafer. While double patterning is effective at increasing feature density, it adds design and patterning complexity along with process steps that consume time, energy, materials, and water – and increase the cost of wafer fabs and wafer production.

To help chipmakers continue shrinking designs without the added cost, complexity, and energy and materials consumption of EUV double patterning, Applied Materials worked closely with leading customers to develop the Centura Sculpta patterning system. Chipmakers can now print a single EUV pattern and then use the Sculpta system to elongate the shapes in any chosen direction to reduce the space between features and increase pattern density. Because the final pattern is created from a single mask, design cost, and complexity are reduced, and the yield risk from double-patterning alignment errors is eliminated.

EUV double patterning requires a number of added manufacturing process steps that generally include CVD patterning film deposition, CMP cleaning, photoresist deposition and removal, EUV lithography, eBeam metrology, patterning film etching, and wafer cleaning. For each EUV double patterning sequence it replaces, the Sculpta system can provide chipmakers with:

- Capital cost savings of approximately $250 million per 100K wafer starts per month of production capacity

- Manufacturing cost savings of approximately $50 per wafer

- Energy savings of more than 15 kWh per wafer

- Direct greenhouse gas emissions reduction of more than 0.35 kg of CO2 equivalent per wafer

- Water savings of approximately 15 liters per wafer

“The new Sculpta system is a great example of how advances in materials engineering can complement EUV lithography to help chipmakers optimize chip area and cost while also tackling the growing economic and environmental challenges of advanced chipmaking,” said Dr. Prabu Raja, Senior Vice President and General Manager of the Semiconductor Products Group at Applied Materials. “The Sculpta system’s unique pattern-shaping technology combines Applied’s deep expertise in ribbon-beam and materials removal technologies to create a breakthrough innovation for the patterning engineer’s toolkit.”

“As Moore’s Law drives us to ever-greater compute performance and density, pattern shaping is proving to be an important new technology that can help reduce manufacturing cost and process complexity, and conserve energy and resources,” said Ryan Russell, corporate vice president for logic technology development at Intel Corp. “Having collaborated closely with Applied Materials in the optimization of Sculpta around our process architecture, Intel will be deploying pattern-shaping capabilities to help us deliver reduced design and manufacturing costs, process cycle times and environmental impact.”

“Three critical issues must be considered when pushing the limits of patterning: tip-to-tip spacing, pattern bridge defects and line edge roughness,” said Jong-Chul Park, Master of Foundry Etch Technology Team at Samsung Electronics. “As an early development partner on the innovative pattern-shaping technology, I believe Applied’s Sculpta system is a fascinating breakthrough that addresses these patterning challenges and reduces manufacturing costs for chipmakers worldwide.”

“Applied Materials’ new Sculpta system is a revolution in patterning that brings an entirely new capability to chipmakers,” said Dan Hutcheson, Vice Chair, TechInsights. “As the industry keeps pushing the limits of chip scaling, we need breakthroughs like Applied’s pattern-shaping technology that can improve chip power, performance, area and cost while also reducing design cost, and energy and materials consumption. Sculpta is the most innovative new process step in wafer fabrication since the introduction of CMP.”

The Sculpta system is receiving high interest from leading chipmakers and has been selected as a production tool of record for multiple steps in high-volume logic manufacturing.