Worlds first 2-nanometer chip technology from IBM. Every decade is a decade to test the limits of Moore’s Law, and this decade is no exception. With the emergence of EUV (Extreme Ultraviolet) technology, the complexity of the multiple template technologies developed in the technology nodes can now be applied with the better resolution provided by EUV.

This and other technological improvements can reduce the size of transistors and open up the future of semiconductors. To this end, IBM has announced that it has developed the world’s first 2 nm chip.

What is Nanometer Technology?

A nanometer also spelled “nanometre”, is a unit of size used to degree length. One nanometer is one-billionth of a meter, so nanometers are now no longer used to degree lengthy distances. Instead, they serve to degree extraordinarily small objects, consisting of atomic systems or transistors located in modern CPUs.

A nanometer is one-billionth of a meter, additionally expressed as 0.000000001 or 10-9 meters. In chip design, “nm” refers back to the duration of a transistor gate – the smaller the gate the greater processing electricity that may be packed right into a given space.

Naming Nodes

To clarify here, although the technology node is referred to as “2 nm”, none of the transistor sizes is close to the traditional 2 nm expectation. For example 90nm, 65nm, and 40nm with the emergence of 3D FinFET and other technologies. The name of the technology node is now an interpretation of the “equivalent 2D transistor” design.

Some functions of the chip may have low single digits in real nanometers, such as the Leakage protection layer on transistor fins. However, it is important to note that the current naming of technology nodes is inconsistent. More accurate indicators, IBM will share with us.

Also Read: TSMC’s 3 nm process facility structure completion, to start production by second half of 2022.

[email-subscribers-form id=”1″]

2 nm Journey

They first proposed the name “Nanosheet” in the summer of 2012 to describe the new device architecture they were working on at the time. Their idea is to design a layered structure that is the opposite of the nanowire structure they use. It was “Aha!” At that time, they thought that the newly named nanosheet structure could provide the electrostatic advantages of nanowires and the density required to improve performance.

Only through this combination of functions, IBM Research can create transistor architecture superior to the main transistor structure FinFET. Their second iteration of nanoplate-based transistor architecture combines a new GAA design with horizontal layers. The four “gates” in the transistor allow stronger electrical signals to pass between other transistors on the chip.

Another “Aha!” on the transition to 2nm was when nanoplates were introduced in 2017. They realized that the internal isolation module in the transistor architecture might improve the nanoplates by reducing the gate capacitance relative to the source/drain. The Inner Spacers are considered to be the critical structural elements because they determine the effective gate length of the GAA devices.

In 2019, the team worked with partner companies to develop a new internal installation process using dry indentation technology. In this way, the process control can be reduced to 1 nm while improving the profile of the lining.

By combining this new internal dry lining process with the industry’s first lower dielectric insulation, they were able to create a 12nm gate that spans only two atoms. There are some benefits of a full bottom dielectric isolation scheme; one of them is sub-channel leakage reduction which provides immunity to offer power-performance improvement and processing variations.

It is important to pay attention to the latest developments in transistor size. For example, 10nm, 7nm, 5nm, and the current 2nm node refer to a specific generation of ICs made using specific types of processing.

Semiconductor manufacturing is similar to 5G which refers to the latest WLAN standard. In this case, for example, 2 nm is not equal to half of the conventionally defined contact metal line pitch. Generally, smaller technology nodes result in smaller transistors whose size is larger than the size of the transistors that can be accommodated on the chip which makes it faster and more energy-efficient.

IBM researchers have also pioneered the use of extreme ultraviolet (EUV) lithography patterns to develop nano-film equipment with a width of 15 to 70 nm, which produces less visible light at the front end of the production line (FEOL).

The first part of integrated circuit manufacturing, where transistors and other components are based on semiconductor modeling. They are the first research organization to talk about the implementation of EUV in FEOL.

The IBM Research Albany Lab showcased one of the most advanced EUV lithography tools in the industry. The ability to more precisely control the width of the nanosheets greatly simplifies the placement of low-power, high-power designs on a single chip.

Another major advancement of the first 2nm transistor is the development of a new Multi-Vt device with a leakage rate exceeding three orders of magnitude, allowing device manufacturers to better choose their performance levels.

In the future, the 2nm processors used in mobile phones can quadruple the battery life of 7nm mobile phones such as the iPhone, Samsung Galaxy S10, and Google Pixel 5. They need to charge every four days.

Compared with the current 7 nm chip with the same performance level, the corresponding performance of the 2 nm transistor extended to the chip node is increased by about 45%. At the same performance level, this is equivalent to saving about 75% of energy.

This combination of functionality and performance is needed to accelerate the development and deployment of advanced cognitive, edge, and other computing platforms delivered via hybrid cloud, as well as cryptographic accelerators designed to be used in conjunction with quantum computers.

IBM Research continues to explore options that can scale to 1 nm or larger. If IBM can continue to provide the hardware that companies can trust, using the latest and most advanced hybrid cloud and artificial intelligence technologies, then bridging these barriers is critical.

Although 2nm node equipment is still several years away from manufacturing, the innovation of IBM Research has a direct impact on our commercial product roadmap. Based on IBM Research in 2015, our first commercial 7nm processor will be unveiled on the IBM POWER10 processor later this year.

Looking ahead, our leadership in semiconductor innovation enables cloud service providers or other large data center operators to reduce energy costs and carbon footprints by reducing the number of servers used for the same workload.

Density of Transistors

Comparison table for Peak Quoted Transistor Densities.

| Peak Quoted Transistor Densities (MTr/mm2) |

| Nanometer | IBM | Intel | TSMC | Samsung |

| 2nm | 333.33 | |||

| 3nm | 292.21* | |||

| 5nm | 171.30 | |||

| 7nm | 237.18* | 91.20 | 95.08 | |

| 10nm | 100.76 | 52.51 | 51.82 | |

| 14/16nm | 44.67 | 28.88 | 33.32 | |

| 22nm | 16.50 |

An announcement was held that points out IBM’s 2nm process technology will increase the performance of the existing performance by 45%, which is 75% higher than the performance of the current 7nm processor.

What IBM would like to point out is that this is the first research institution to demonstrate 7 nm in 2015 and 5 nm in 2017. The latter is upgraded to nanoplate technology through FinFETs, which can further adjust the voltage characteristics of each transistor.

IBM claims that the technology can hold “50 billion transistors on a nail chip.” Some interviewers contacted IBM to clarify the size of the nails because internally, the size of the nails they received varied from 50 square millimeters to 250 square mm. IBM’s media contact indicated that in this case, the nail is 150 square millimeters, which means that the density of IBM transistors is 333 million transistors per square millimeter (MTr/mm2).

As you can see, different foundries have different official names with different densities. It should be noted that these density values are usually given as the maximum density of the transistor library, where matrix area is the main issue, not the frequency range, which is usually the fastest part of the processor. Due to heat and electricity issues, their height is only half of the latter.

Regarding the switch to the all-round gate/nanochip, the new 2nm processor uses a three-layer GAA design, although IBM did not specify it. Samsung introduced GAA at 3 nm, while Taiwan Semiconductor Manufacturing Company (TSMC) expects it to reach 2 nm. On the contrary, we believe that Intel will introduce some form of GAA in its 5nm process.

The unit height used by IBM 3-Stack GAA is 75 nm, the unit width is 40 nm, the height of a single nano plastic is 5 nm, and the distance is 5 nm. The polygonal gate pitch is 44 nm and the gate length is 12 nm.

According to IBM, a lower dielectric isolation channel is used for the first time, and the gate length is 12 nm. The internal isolation layer is a second-generation dry process design. This helps for the development of nano blades. The EUV mode is used in part of the FEOL process, which allows EUV to be used in all stages of the key layer design.

Users like you and me may wonder why they heard that IBM was the first company to use 2nm chips. IBM is one of the world’s leading research centers for future semiconductor technology. Although there is no proprietary product, IBM cooperated to develop intellectual property rights and sold its manufactured products to GlobalFoundries in 2014 with a ten-year partnership.

IBM is currently also cooperating with Samsung and recently announced a partnership with Intel. Because of its viability in its production chain, it can keep pace with this new development project.

Although the 2nm test chip may not have any logical details at this time, detailed information is still provided in test cases to confirm the feasibility of the technology. According to IBM, the test project uses a multi-virtual terminal design to demonstrate powerful and efficient applications.

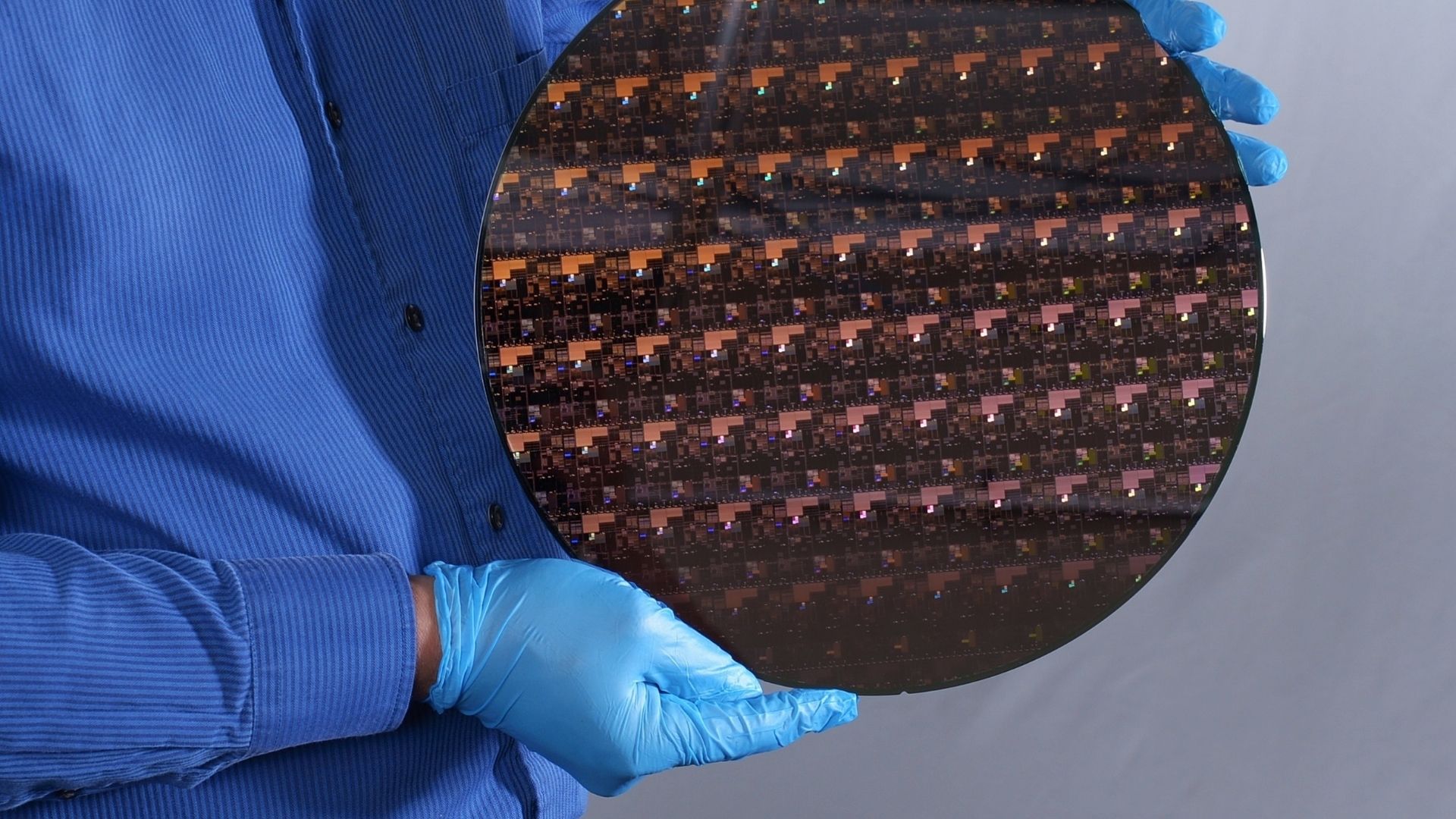

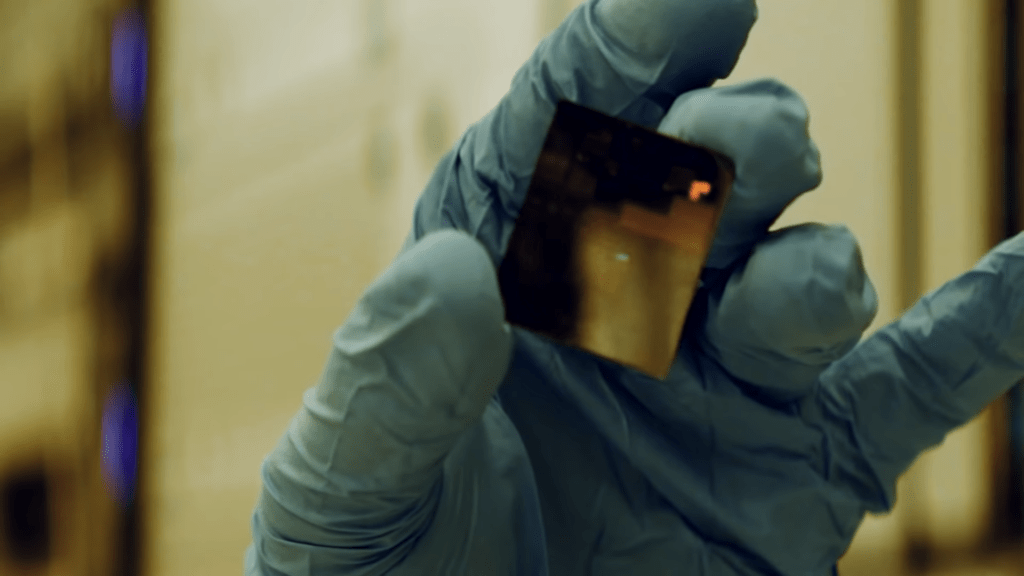

The chip was designed and manufactured at the IBM Research Center in Albany, which has a cleanroom of 100,000 square meters. The purpose of this setting is to use IBM’s extensive patent and licensing portfolio to work with partners.

About IBM

IBM stands for International Business Machines. IBM is one of the largest information technology companies in the world and it provides a wide range of software, hardware, and services.

IBM started as an equipment manufacturer and has been in this business for decades. Become a leading mainframe provider. Over the years, the company has also started to focus on hardware to software and services.

In the 2010s, IBM further transformed its business portfolio and focused on cloud services and cognitive computing. In this part of the latest technology, the cognitive system has become the company’s most obvious proposition.